Принципы построения параллельных портов

(слайд 17).Параллельные портыпредназначены для обмена многоразрядными двоичными данными между МП и ВУ. (слайд 18). В качестве ВУ может выступатьлюбой объект управления или источник информации (различные кнопки, датчики; микросхемы приемников, синтезаторов частот, дополнительной памяти; исполнительные механизмы, двигатели, реле и т. д.). Иногда в качестве ВУ может выступать другой компьютер или МПС.

Параллельные порты позволяют согласовывать низкую скорость работы ВУ и высокую скорость работы системной шины МП. С точки зрения ВУ порт представляет собой обычный источник или приемник информации со стандартными цифровыми логическими уровнями (обычно ТТЛ), а с точки зрения микропроцессора это ячейка памяти, куда можно записывать данные или где сама собой появляется информация.

(слайд 19). В зависимости от направления передачи данных параллельные порты называются портами ввода, портами вывода или портами ввода-вывода информации.

Одной из основных функций параллельного порта является ввод информации с кнопок или механических датчиков. Иногда требуется вводить информацию с очень большого количества кнопок. В этом случае для уменьшения количества линий ввода параллельного порта используется клавиатура, представляющая собой двухмерную матрицу кнопок, организованных в ряды и колонки.

3.1 Параллельный порт вывода

Простейший порт вывода может быть построен на базе параллельного регистра, т. к. это устройство позволяет запоминать данные, передаваемые микропроцессором по системной шине, и хранить их до тех пор, пока на МПС подается питание. Все это время сигналы с выходов параллельного регистра подаются на ВУ (или сразу на несколько ВУ). Принципиальная схема простейшего порта вывода с использованием параллельного регистра приведена на рисунке 11.4.

|

|

|

Данные с системной шины микропроцессора записываются в параллельный регистр по сигналу записи  . Это становится возможным только при наличии нулевого уровня на выходе дешифратора адреса. Как мы уже рассматривали ранее, логическую функцию "2И" с инверсией сигналов на входе можно заменить на логическую функцию "2ИЛИ", что, и показано на рисунке 11.4.

. Это становится возможным только при наличии нулевого уровня на выходе дешифратора адреса. Как мы уже рассматривали ранее, логическую функцию "2И" с инверсией сигналов на входе можно заменить на логическую функцию "2ИЛИ", что, и показано на рисунке 11.4.

Выходы " Q " регистра могут быть использованы как источники логических уровней для управления ВУ. Этот регистр называется регистром данных порта вывода. Иногда, для упрощения схемы МПУ, в состав параллельного порта включаются силовые транзисторные ключи, подключенные к выходам регистра. Схема параллельного порта при этом несколько усложняется.

В порт вывода, построенный по схеме, приведенной на рисунке 11.4, возможна только запись двоичного многоразрядного числа. Так как в данной схеме нет цепей чтения содержимого регистра данных, то чтение его содержимого микропроцессором становится невозможным. Это не следует считать недостатком, т. к. копия содержимого регистра данных порта вывода обычно хранится в ОЗУ.

|

|

|

Для отображения регистра данных параллельного порта вывода информации только в одну ячейку памяти адресного пространства МПУ, а не во все адресное пространство МПС, совместно с портом вывода всегда используется дешифратор адреса.

(слайд 20).

Рисунок 11.4 – Принципиальная схема порта вывода

3.2 Параллельный порт ввода

Задача порта ввода дискретной информации является обратной по отношению к задаче порта вывода. В данном случае логические сигналы, поступающие с ВУ, необходимо подключать к ШД системной шины по сигналу запроса  от микропроцессора. Все остальное время сигналы, формируемые ВУ, не должны мешать нормальной работе МПС.

от микропроцессора. Все остальное время сигналы, формируемые ВУ, не должны мешать нормальной работе МПС.

В качестве порта ввода обычно используются схемы с третьим (Z) состоянием. Микросхема, объединяющая несколько таких элементов, называется шинным формирователем (ШФ). Из порта ввода возможно только чтение информации. Структурная схема простейшего порта ввода приведена на рисунке 11.5. Для построения порта ввода, выход ШФ подключается к внутренней шине данных (ВШД), а к его входу подводятся сигналы, которые требуется контролировать МПС. Значение сигнала с внешнего вывода порта передается на ШД (учитывается) по управляющему сигналу  .

.

|

|

|

(слайд 21).

Рисунок 11.5 – Структурная схема порта ввода

Для отображения ШФ порта ввода только в один адрес в пространстве адресов МПУ совместно с портом ввода используют дешифратор адреса. Так как с точки зрения программиста эта ячейка памяти ничем не отличается от регистра данных порта вывода, то по аналогии она называется регистром данных порта ввода.

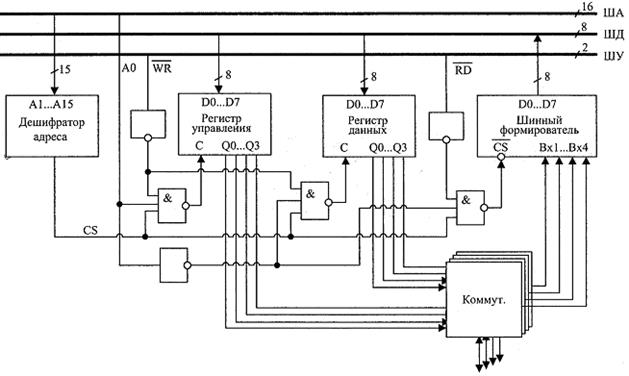

3.3 Параллельный порт ввода-вывода

В одной универсальной микросхеме могут размещаться и порт ввода, и порт вывода информации одновременно. Конечному пользователю при этом предоставляют возможность настройки линий порта на ввод или вывод информации. Такие порты называются портами ввода-вывода информации. Структурная схема параллельного порта ввода-вывода приведена на рисунке 11.6.

Из порта ввода возможно только чтение, а в порт вывода возможна только запись данных, поэтому в адресном пространстве микропроцессора для порта ввода и порта вывода можно назначать один и тот же адрес. В рисунке 11.6 регистр данных и ШФ тоже используют один и тот же адрес. Это обеспечивается подачей на вход логических элементов "3И-НЕ" одного и того же потенциала из линии А0. Какое из устройств в данный момент будет подключено к ШД, определяется сигналами записи  и чтения

и чтения  .

.

|

|

|

Для подключения портов ввода или портов вывода информации к внешним выводам микросхемы в схеме используется коммутатор. Именно он определяет направление передачи данных. Управляет этим коммутатором еще один (внутренний) параллельный порт вывода, регистр данных которого называется регистром управления параллельного порта ввода-вывода. Регистру управления и регистрам данных порта ввода-вывода обычно назначаются соседние адреса. На приведенной схеме это обеспечивается инверсией линии младшего разряда адреса А0.

(слайд 22).

Рисунок 11.6 – Структурная схема параллельного порта ввода-вывода

В схеме можно было обеспечить чтение внутренней информации регистра управления, подключив еще один ШФ (что обычно и делается), однако это бы уменьшило наглядность рисунка, поэтому эта возможность в схеме, приведенной на рисунке 11.6, отсутствует.

Следует отметить, что обычно то, что регистр управления подключается через внутренний параллельный порт, не указывается, и вся схема в целом называется портом ввода-вывода.

В некоторых микропроцессорах для портов ввода-вывода выделяется отдельное адресное пространство. В этом случае для записи в порт и для чтения из порта используются отдельные сигналы чтения и записи. Чаще всего они называются "IOWR#" и "IORD#". В этом названии буквы IО означают ввод-вывод (input-output), а знак # – использование активного нулевого потенциала (как в рассмотренных ранее сигналах записи и чтения памяти МПС). Применение подобного символа позволяет избежать использования черты над названием цепи, что неприменимо для ряда современных редакторов схем.

Параллельные порты используются также для обмена данными между компьютерами и компьютером и принтером.

Дата добавления: 2022-01-22; просмотров: 24; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!