Лабораторные работы № 5, 6, 7

Тема: Исследование регистров, счетчиков и цифровых запоминающих устройств.

Цель работы:

– изучение схем и принципов работы регистров, счетчиков и цифровых запоминающих устройств;

– исследование счетчика и регистра на интегральных микросхемах.

Теоретические сведения

Регистры и счетчики относятся к цифровым устройствам. Они широко используются для построения устройств ввода, вывода и хранения информации, а также для выполнения некоторых арифметических и логических операций.

Для построения счетчиков и регистров используются синхронные триггеры, переключение которых происходит только при наличии синхронизирующего сигнала(синхроимпульса) на входе С. Наиболее часто для построения регистров и счетчиков используются универсальный D-триггер, имеющий специальный информационный вход D, синхронизирующий вход С, вход S – установки в 1 и вход R – установки в 0 (рис.1). Например, микросхема К155ТМ2(аналог SN7474) содержит два таких триггера. Запись информации в них производиться по переднему фронту синхроимпульса.

Рис. 1

Устройство, называемое регистром, служит в основном для хранения чисел в двоичном коде при выполнении над ними различных арифметических и логических операций. С помощью регистров выполняются такие действия над числами, как передача их из одного устройства в другое, арифметический и логический сдвиг в сторону младших или старших разрядов, преобразование кода из последовательного в параллельный и наоборот и т.д. Функциональная схема и условно-графическое обозначение трехразрядного регистра параллельного типа, собранного на универсальных D-триггерах, приведена на рис.2

|

|

|

Рис. 2

По синхроимпульсу на входе С информация (двоичное трехразрядное слово), поступившая на входы D1-D3, записывается в регистр и храниться в нем до тех пор, пока не произойдет запись другой информации, либо не поступит сигнал на вход R, обнуляющий регистр.

Информацию из регистра можно прочитать с выходов Q1-Q3

Функциональная схема и условно-графическое обозначение трехразрядного регистра сдвига представлены на рис.3.

Рис. 3

Последовательный информационный двоичный код поступает поразрядно на вход D регистра. Импульс сдвига С подается одновременно на синхронизирующие входы всех триггеров регистра и переводит каждый триггер в состояние, в котором находился триггер предыдущего разряда. Таким образом, каждый импульс команды сдвига «продвигает» записываемое число на один разряд вправо.

Существуют реверсивные регистры сдвига, позволяющие сдвигать информацию и вправо, и влево, а также регистры сдвига, позволяющие принимать и параллельный и последовательный входной код.

|

|

|

Устройство, называемое счетчиком, предназначено для подсчета числа поступающих на вход импульсов в произвольной системе счисления.

Двоичные счетчики строятся на основе триггеров, работающих в счетном режиме (Т-триггер или счетный триггер).

Счетные триггер может быть получен из универсального D-триггера путем соединения его инверсного выхода 0 со входом D.

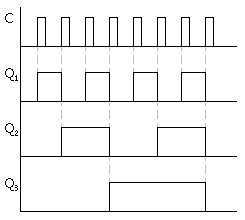

Счетный триггер и эпюры сигналов, поясняющие его работу, представлены на рис.4.

Рис. 4

У счетного триггера состояние выхода изменяется на противоположное при поступлении на вход С каждого очередного счетного импульса.

Функциональная схема и условное графическое обозначение двоичного счетчика с коэффициентом пересчета 23 представлена на рис.5.

Рис. 5

Каждый поступающий на вход счетчика импульс перебрасывает первый триггер в противоположное состояние (рис.6). Сигнал с инверсного выхода предыдущего триггера является входным сигналов для последующего и, таким образом, комбинация сигналов на выходах Q1,Q2,Q3 будет соответствовать числу поступивших на вход счетчика импульсов, представленному в двоичном коде.

|

|

|

Рис. 6

Если на счетный вход последующего триггера счетчика подавать сигнал с прямого выхода предыдущего триггера, то счетчик будет производить операцию вычитания. Счетчики, способные выполнять функции суммирования и вычитания, называются реверсивными.

Для построения счетчика с требуемым коэффициентом пересчета М, отличным от величины 2N (N – число двоичных разрядов счетчика), используется принудительный сброс счетчика в исходное состояние при достижении счетчиком числа М.

Запоминающие устройства, в которых в качестве запоминающих ячеек используются параллельные регистры, называются статическими оперативными запоминающими устройствами (ОЗУ), т.к. информация в них сохраняется все время, пока к микросхеме подключено питание. В отличие от статических ОЗУ в микросхемах динамического ОЗУ постоянно требуется регенерировать их содержимое, иначе информация будет потеряна.

В микросхемах ОЗУ присутствуют две операции: операция записи и операция чтения. Для записи и чтения информации можно использовать различные шины, но чаще используется одна и та же шина данных. Это позволяет экономить выводы микросхем, подключаемых к этой шине и легко осуществлять коммутацию сигналов между различными устройствами.

|

|

|

Схема статического ОЗУ приведена на рисунке 7. Вход и выход микросхемы в этой схеме объединены при помощи шинного формирователя. Естественно, что схемы реальных ОЗУ будут отличаться от приведенной на этом рисунке. Тем не менее, приведенная схема позволяет понять как работает реальное ОЗУ. Изображение ОЗУ на принципиальных схемах приведено на рисунке 8.

Рисунок 7. Структурная схема ОЗУ.

Рисунок 8. Изображение ОЗУ на принципиальных схемах.

Сигнал записи WR позволяет записать логические уровни, присутствующие на информационных входах во внутреннюю ячейку ОЗУ. Сигнал чтения RD позволяет выдать содержимое внутренней ячейки памяти на информационные выходы микросхемы. В приведенной на рисунке 7 схеме невозможно одновременно производить операцию записи и чтения, но обычно это и не нужно.

Конкретная ячейка микросхемы выбирается при помощи двоичного кода - адреса ячейки. Объем памяти микросхемы зависит от количества ячеек, содержащихся в ней или, что то же самое, от количества адресных проводов. Количество ячеек в микросхеме можно определить по количеству адресных проводов возводя 2 в степень, равную количеству адресных выводов в микросхеме:

Вывод выбора кристалла CS позволяет объединять несколько микросхем для увеличения объема памяти ОЗУ. Такая схема приведена на рисунке 9.

Рисунок 9. Схема ОЗУ, построенного на нескольких микросхемах памяти.

Статические ОЗУ требуют для своего построения большой площади кристалла, поэтому их ёмкость относительно невелика. Статические ОЗУ применяются для построения микроконтроллерных схем из-за простоты построения принципиальной схемы. Кроме того статические ОЗУ применяются для построения КЭШ-памяти в универсальных компьютерах из-за высокого быстродействия статического ОЗУ.

Статические оперативные запоминающие устройства позволяют обеспечивать хранение записанной информации до тех пор, пока на микросхему подаётся питание. Однако запоминающая ячейка статического ОЗУ занимает относительно большую площадь, поэтому для ОЗУ большого объема в качестве запоминающей ячейки применяют конденсатор. Заряд на этой ёмкости естественно с течением времени уменьшается, поэтому его необходимо подзаряжать с периодом приблизительно 10 мс. Этот период называется периодом регенерации. Подзарядка ёмкости производится при считывании ячейки памяти, поэтому для регенерации информации достаточно просто считать регенерируемую ячейку памяти.

Схема запоминающего элемента динамического ОЗУ и его конструкция приведена на рисунке 10.

Рисунок 10. Схема запоминающего элемента динамического ОЗУ и его конструкция.

Особенностью динамических ОЗУ является мультиплексирование шины адреса. Адрес строки и адрес столбца передаются поочередно. Адрес строки синхронизируется стробирующим сигналом RAS# (Row Address strobe), а адрес столбца - CAS# (Column Adress Strobe). Мультиплексирование адресов позволяет уменьшить количество ножек микросхем ОЗУ. Изображение микросхемы динамического ОЗУ приведено на рисунке 11.

Рисунок 11. Изображение динамического ОЗУ на принципиальных схемах.

ЗАДАНИЕ

1. Используя компоненты Electronics Workbench, соберите схему для исследования четырехразрядного регистра сдвига, представленную на рис.12.

Рис. 12

В этой схеме регистр сдвига собран на четырех D-триггерах, состояние которых индицируется лампочками Q1..Q4.

На последовательный вход регистра подается логический 0 или 1 с переключателя D. С генератора одиночного импульса, собранного на переключателе С, двух резисторах 1кОм и двух элементах И-НЕ, при каждом переключении переключателя С из 0 в 1 и обратно, выдается один синхроимпульс сдвига, очищенный от дребезга контактов.

Включите схему. Подайте логическую 1 на вход D регистра и затем один синхроимпульс на вход С. Подайте логический 0 на вход D регистра. Подайте еще 3 синхроимпульса, наблюдая за состоянием триггеров. Составьте временную диаграмму. Пронаблюдайте запись в регистр и прохождение через него других двоичных кодов. Составьте временные диаграммы.

2. Используя компоненты Electronics Workbench соберите схему трехразрядного двоичного счетчика, представленного на рис.5

Подключите ко входу С счетчика генератор прямоугольных импульсов амплитудой 5В и частотой 0,2…1Гц. Для индикации состояния генератора и триггеров, к их выходам подключите лампочки или светодиоды с ограничительными резисторами 330 Ом. Включите схему, составьте таблицу изменения состояний триггеров, начиная с состояний Q1=Q2=Q3=0. Зарисуйте временную диаграмму работы двоичного счетчика.

Для удобства наблюдений работу схемы можно приостанавливать нажатием кнопки PAUSE, а при использовании триггеров с R-входом и дополнительного переключателя сброса, счетчик можно обнулять, не дожидаясь его периодического самообнуления.

3. Соберите схему, представленную на рис.13, для исследования двоично-десятичного счетчика. Схема собирается на двух конкретных микросхемах:

– SN7400 (аналог К155ЛА3, содержит 4 элемента 2И-НЕ)

– SN7490 (аналог К155ИЕ2, содержит двоично-десятичный четырехразрядный счетчик с инверсным динамическим входом)

Кроме того, схема содержит источник питания(5В), переключатель R сброса счетчика в ноль, переключатель С подачи одиночного импульса, лампочки индикации состояний счетчика (1,2,4,8) и его входа(С), резисторы и светодиодный семисегментный индикатор со встроенным дешифратором двоично-десятичного кода в семисегментный код.

Рис. 13

На микросхеме 7400(используется ее половина) собран асинхронный RS-триггер, который вместе с переключателем С и двумя резисторами 1кОм, образует генератор одиночного импульса. Микросхема 7490 содержит четыре счетных триггера, причем первый из них (А) отделен от остальных трех(B,C,D), которые соединены так, что образуют счетчик с модулем счета 5. Поэтому чтобы получить десятичный счетчик (с модулем счета 10) необходимо выход QA первого триггера соединить со счетным входом СКВ второго триггера. Таким образом, входом двоично-десятичного четырех разрядного счетчика будет вход СКА(вывод 14), а выходами QA, QB, QC, QD с «весами» соответственно: 20=1, 21=2, 22=4, 23=8. Состояние счетчика в двоичном коде отображают лампочки 1,2,4,8, а в десятичном коде-семисегментный индикатор.

Включите схему. Исследуйте работу счетчика, устанавливая переключатель С попеременно в 1 и 0. Заполните таблицу состояний триггеров в зависимости от номера входного импульса. Составьте временную диаграмму работы счетчика. Сбросить счетчик в 0 можно ключом R.

4. Вместо генератора одиночного импульса подключите ко входу СКА счетчика (Вывод 14) генератор прямоугольных импульсов, амплитудой +5В и частотой 1…2Гц. Наблюдайте за изменением состояний лампочек и индикатора, пока принцип работы счетчика не станет ясен.

Замечание. На практике часто применяют дешифраторы четырехразрядного двоичного кода в семисегментный выполненные в виде отдельных микросхем (например, SN7447, SN7448, К514ИД1, К514ИД2), которые подключают к семисегментным светодиодным индикаторам, не имеющим дешифраторов (например, MAN-1, АЛС-321, АЛС-324, АЛС-333).

5. Подключите к выходу генератора и к выходам QA, QB, QC, QD счетчика анализатор логических сигналов (Logic Analyzer), предназначенный для индикации двоичных слов, с помощи кнопки Set установите внутреннюю частоту прибора выше частоты генератора импульсов, а число импульсов на деление (Clocks per division) для удобства наблюдения сделайте равным 1-4. Анализатор позволяет существенно облегчить составление временных диаграмм и отладку цифровых схем.

Рекомендуемая литература

Основная литература:

1. Немцов М.В. Электротехника и электроника. / М.В.Немцов, М.Л.Немцова - М: Академия,2014

2. Мышляева И.М. «Цифровая Схемотехника» учебник 2012г. Издательство: «Академия» п. 400с.

3. Павлов В.Н. «Схемотехника аналоговых электронных устройств»

4. Новиков Ю.В. «Введение в цифровую схемотехнику» Издательство:

5. Бином. Лаборатория знаний 2012 г.

6. Медведев Б.Л., Пирогов Л.Г. «Практическое пособие по цифровой схемотехнике» Издательство: Мир 2012г.

7. Немцов М.В., Немцова М.Л. Электротехника и электроника. М: Академия, 2007

Дополнительная литература:

8. Синдеев Ю.Г. Электротехника с основами электроники. Ростов-на- Дону: Феникс, 2010, 416с

9. Бутырин П.А. Электротехника . Учебник. НПО , - М.: ИЦ "Академия", 2007 4-е изд.

10. Клиначёв Н.В. Учебно-методический комплекс «Электрические цепи постоянного тока». 1999-2012. Ьпр://пюс1е1.ехропел1а.ги/е1есЦо/0022.1цт.

11. Угрюмов Е.П. Цифровая схемотехника Учеб.пособие для вузов. Изд.2, БХВ-Петербург, 2011.

12. Бабич Николай «Основы цифровой схемотехники»: Учебное пособие Издательство: Додэка-ХХ1 2007г.

13. Волович Г.И. «Схемотехника аналоговых и аналого-цифровых электронных устройств» Издательство: Додэка-ХХ1 2007г.

14. Электронные ресурс «Общая электроника и электротехника». Форма доступа: Нир://1ое.к1('.тгхи.ги/с1ето_уегаа/.

15. Лаврентьев Б.Ф. Схемотехника электронных средств. Уч. пособ. – М.: изд-во «Академия», 2010. - 336 с.

16. Основы электроники. Учебное пособие для вузов / А. Л. Марченко.— М. : ДМК Пресс,

2008

17. Галле К. Силовая электроника. Как проектировать электронные схемы. 2009 год. 202 стр.

18. Титце У., Шенк К. Полупроводниковая схемотехника. 12-е изд. 2008 год. Том1. 832 стр. djvu. 5.9 Мб. Том 2.942 стр. PDF. 65.1 Мб.

19. Лачин В.И., Савёлов Н.С. Электроника. Учебное пособие.- Ростов н/Д: изд-во «Феникс», 2007- 576 с. (Серия «Высшее образование»).

20. Сиднев Ю.Г. электротехника с основами электроники. Учебн. пособие. -3-е издание- Ростов н/Д.: Феникс.- 2002.- 384 с.

21. Амосов В.В. Схемотехника и средства проектирования цифровых устройств. 2007 год. 542 стр. pdf.

Дата добавления: 2019-11-16; просмотров: 547; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!