Если 3 бит селектора команды равен 0, то индекс селектора относится к таблице LDT.

В этом случае процедура отображения виртуального адреса в физический имеет отличия:

2.1. По содержимому регистра LDTR находится дескриптор таблицы LDT в таблице GDT.

2.2. В дескрипторе находится базовый адрес таблицы LDT в ОЗУ.

2.3. По содержимому индекса команды в таблице LDT находится дескриптор сегмента (физический адрес).

Далее выполняются операции, как и для случая с GDT.

Сравнение уровней привилегий селектора команды RPL и дескриптора DPL обеспечивает защиту сегментов в ОЗУ

Одним из существенных достоинств и отличий сегментной организации памяти от страничной является возможность задания дифференцированных прав доступа процесса к его сегментам.

Например, один сегмент данных, содержащий исходную информацию для приложения, может иметь права доступа «только чтение», а сегмент данных, представляющий результаты, - «чтение и запись».

Это свойство означает принципиальное преимущество сегментной модели памяти над страничной

Контроль размеров сегментов в виртуальной сегментной памяти (т.е. в защищенном режиме) является важным фактором надежности защиты сегментов от взаимного влияния.

Недостатки сегментной адресации:

Недостатком сегментного распределения является избыточность.

При сегментной организации единицей перемещения между памятью и диском является сегмент, имеющий в общем случае объем больший, чем страница.

Однако во многих случаях для работы программы вовсе не требуется загружать весь сегмент целиком, достаточно было бы одной или двух страниц.

Аналогично, при отсутствии свободного места в памяти не стоит выгружать целый сегмент, когда можно обойтись выгрузкой нескольких страниц.

Однако главный недостаток сегментного распределения - это фрагментация, которая возникает из-за непредсказуемости размеров сегментов.

Регистры процессоров, участвующие в управлении виртуальной

Памятью и системными процессами

Регистры системных адресов

К регистрам системных адресов относятся GDTR, LDTR, IDTR, TR.

Доступ к ним возможен на уровне привилегий ядра ОС (высшего 0 уровня ).

Имеются команды загрузки этих регистров: LLDT, LGDT, LIDT, LTR (типа LDS, LES ).

Регистр GDTR 48 – разрядный.

32 разряда (16 – 47 ) отведены под базовый адрес сегмента, в котором размещена таблица дескрипторов сегментов GDT и 16 ( 0-15 ) под указатель размера сегмента в байтах (! что мало).

Регистр LDTR содержит 16 разрядный селектор базового адреса таблицы дескрипторов сегментов LDT в таблице GDT.

Регистр IDTR по структуре аналогичен регистру GDTR.

Содержит базовый адрес таблицы векторов прерываний.

Регистр TR – task register содержит 16 разрядный селектор базового адреса текущего сегмента TSS (task system state).

Системные регистры CR0-CR4

32 р. регистры CRO-CR4 относятся к управляющим.

Их биты управляют режимами работы процессора.

Системным программистам они доступны с помощью специальных команд, через которые производится загрузка в РОНЫ.

Регистр CR0.

Содержит биты, управляющие режимами микропроцессора (реальный, защищенный ), включением страничной адресации, режимами работы КЭШ и сопроцессора, и относящие к системе в целом.

Первые 16 бит называются словом состояния машины (MSW – machine state word).

PE – protect enable - бит переключения в защищенный режим.

MP – math present – разрешение работы с сопроцессором.

EM – emulation math - эмуляция сопроцессора.

TS - task switched - переключение задач.

Устанавливается в 1 при каждом переключении задач.

Очищается специальной командой CLTS.

ET - extension - поддержка команд FPU.

В новых процессорах всегда 1.

NE - numeric error – разрешение сообщений error FPU.

WP - write protect запрет записи в страницу пользователя из ОС при WP =1 (read only).

AM - alignment mask – разрешение контроля выравнивания ( по битам – чет /нечет ).

При обращениях к памяти двойное слово должно начинаться с адреса, кратного 4, а 2 байтное – кратное 2.

NW – not write through – запрет сквозной записи КЭШ.

CD – cache disable - запрет КЭШ.

PG - page enable – включение страничной поддержки.

Используется в защищенном режиме.

Указывает на то, что для трансляции линейных адресов в физические используется таблица страниц.

При МР = 0, ЕМ = 0, TS = 0 обеспечивается полная совместимость с 8086 и 8088.

2. Регистр CR1.Резервный.

Регистр CR2.

Используется для слежения за корректным обращением к страницам и выдачей сообщений (нет в ОЗУ, нарушение прав доступа, отказы стр и др. ), если используется страничная адресация(если в регистре CR0 активен бит PG = 1).

В нем сохраняется линейный адрес, который вызвал исключение.

Код ошибки в стеке обработчика нарушения.

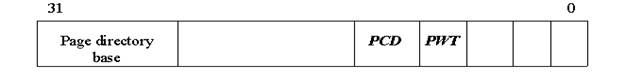

Регистр CR3.

Это регистр каталога страниц.

Он еще называется PDBR (page directory base registr).

Содержит базовый адрес каталога страниц РDE для текущей задачи.

В старших 10 битах – базовый адрес каталога страниц.

Всегда выравнивается на размер страниц 4Кб.

Регистр CR3 активен только, если в регистре CR0 активен бит PG = 1.

Биты 3 и 4 управляют кэшированием страниц.

PCD – page cache disable – запрет КЭШ страниц.

PWT – page writes through – кэширование страниц со сквозной записью.

Регистр CR4.

Биты этого регистра управляют некоторыми архитектурными элементами компьюте- ра:

* переключение флагов в режим виртуального V86;

* изменение размера страниц;

* расширение адресного пространства процессора;

и др.

Биты:

VME - VIRTUAL 8086 mode extension – разрешение использования флагов в режиме виртуального V86.

Позволяет обрабатывать прерывания не переключаясь в защищенный режим.

Поддерживает бит виртуального флага прерывания VIF.

PVI - protected mode virtual interrupt- разрешение использования виртуального флага прерывания в защищенном режиме.

TSD - time stamp disable – превращение команды чтения счетчика меток реального времени ( RDTSC ) в привилегированную.

DE - debugging extension – разрешение отладки ( точек останова ).

PSE – page size extension - расширение размера страниц .

PAE – physical address extension - расширение физического адреса.

MCE - machine check enable -разрешение машинного контроля .

PGE - paging global extension - разрешение глобальности в страницах переадресации (PDE/PTE).

Часто используемые страницы отмечаются как глобальные и не выгружаются при переключении задач.

PCE - performance monitoring counter enable – разрешение обращения к счетчикам событий на любом уровне привилегий.

Какими возможностями обладает процессор можно узнать командой CPUID.

Общие регистры CPU и FPU

1.РОН

EAX, EBX, ECX, EDX, EDI, ESI, EBР, ESP.

2. EIP(instruction pointer).

3. CS, DS, SS, ES, FS, GS.

Дата добавления: 2018-08-06; просмотров: 273; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!