II. Структура системы автоматического регулирования (САР).

2. Структурная схема САР.

Данная система для удобства отображения построена по иерархическому принципу. Её структурная схема содержит основные компоненты, которые по иерархическому принципу содержат в себе другие компоненты, которые могут содержать в и 3-й уровень компонентов схемы. Это сделано для удобства реализации самой схемы. Реализация элементов системы подчиняется «принципу матрешки».

Общий вид САР представлен на рис. 2. На рисунке изображены следующие управляющие элементы и элементы индикации:

– Управляющие элементы:

Programm_Vz – задатчик, в котором должна быть записана программа изменения уставок во времени;

Peredacha – модель передающей стороны системы телемеханики (поста управления);

Line – модель канала связи;

Priyem – модель приемной стороны системы телемеханики (линейного пункта);

Local_SAR – модель локальной системы автоматического регулирования технологического параметра;

Vnesh_vozm – модель внешних возмущений на объект регулирования;

С – генератор тактовых импульсов для автоматического формирования различных ошибок в канале связи;

Kratnost – элемент настройки кратности автоматически подсчитываемых ошибок в канале связи;

– Элементы индикации:

Code_out – индикатор отправляемого передающей стороной в канал связи сообщения в заданном помехозащитном коде;

Code_in – индикатор принятого приемной стороной сообщения в заданном помехозащитном коде;

|

|

|

Result – индикатор подсчитанного количества ошибок заданной элементом Kreatnost кратности в двоичном коде.

OU – осциллограф для отображения процесса регулирования технологического параметра объекта регулирования локальной системой автоматического регулирования.

3. Структурная схема блока Peredacha.

Блок Peredacha (рис.3) представляет собой модель поста телеуправления. В различные моменты времени находящийся на посту управления программный задатчик Programm_Vz формирует соответствующие требуемые значения регулируемого технологического параметра Vz.

Блок Peredacha (рис.3) представляет собой модель поста телеуправления. В различные моменты времени находящийся на посту управления программный задатчик Programm_Vz формирует соответствующие требуемые значения регулируемого технологического параметра Vz.

Рис. 3. Блок Peredacha.

Состав блока Peredacha.:

Commands (1 of N) – дешифратор команд. Схема дешифратора изображена на рис.4. Выходной сигнал элемента представлен в коде 1 из N, где N – шестнадцатеричный номер команды. Дешифратор команд позволяет определить текущую команду, формируемую задатчиком. На вход поступает значение уставки от 1 до 15. В зависимости от значения уставки, срабатывает схема сравнения (в каждом звене этой схемы записан эквивалент определенного числа, в нашем случае от 1 до 15). В случае совпадения значения подаваемой уставки и эквивалента в схеме сравнения, на выходе ячейки схемы сравнения мы будем иметь логическую единицу.

|

|

|

Рис. 4. Дешифратор команд.

Код «1 из N» означает, что только на одном выходе дешифратора присутствует логическая единица (соответствующая передаваемой команде), а на остальных выходах присутствует ноль.

Coder 2^n – кодер обыкновенного двоичного кода (рис.5). Преобразует код «1 из N» в код «2^n» (обыкновенный двоичный код). Данный кодер формирует информационную часть разделимого кода, которая по сути представляет двоичный код номера передаваемой команды. Состоит из элементов OR (ИЛИ). При подаче на хотя бы один из входов, элемента логической единицы, на выходе получим логическую единицу. К примеру число 9 соответствует логической единице на входе 9. Имеем  , что соответствует

, что соответствует  .

.

Рис. 4 Кодер обыкновенного кода 2^n.

Coder_izb_code – кодер контрольной части разделимого кода построен по принципу кодирования модифицированным кодом Хэмминга и вычисляет значения контрольных разрядов кода. Кодер построен на элементах XOR (исключающее ИЛИ) (Рис.5)

Рисунок 5. Логический элемент XOR (исключающее ИЛИ).

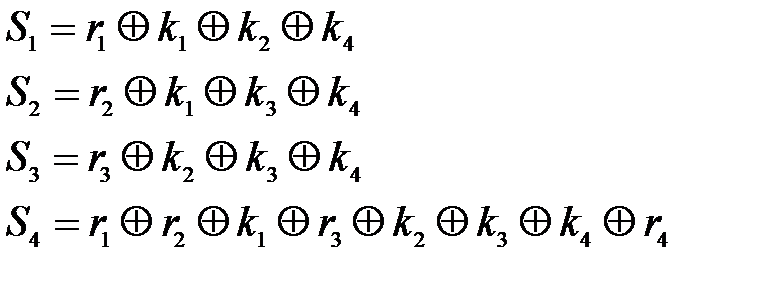

Принцип кодирования контрольных значений, заложенный в моей схеме заложен в данных формулах:

Схема кодера контрольной части разделимого кода изображена на рис.6.

Рисунок 6. Схема кодера контрольной части разделимого модифицированного кода Хэмминга.

|

|

|

Кроме управляющих элементов на схеме приведены индикаторы, для контроля правильности работы управляющих элементов.

4. Структурная схема линии связи с искажениями.

Модель линии связи с искажениями изображена на рис. 7.

Рисунок 7. Модель линии связи с искажениями.

CD – двоичный восьмиразрядный счетчик для моделирования искажений различной кратности (рис.8). На вход С поступает сигнал с генератора прямоугольных импульсов С для автоматического формирования ошибок с некоторой кратностью.

Элементы XOR – каждый элемент в зависимости от управляющего сигнала, поступающего с соответствующего выхода счетчика, инвертирует, либо повторяет входной сигнал на своем выходе. Таким образом, элементы XOR позволяют вносить различные искажения в передаваемые по линии связи сообщения. Кратность искажения определяется количеством логических единиц на выходах счетчика CD.

Рисунок 8. CD – двоичный восьмиразрядный счетчик.

Error_counter – счетчик с выходным сигналом в виде десятичного числа (рис.9), показывающего кратность внесенной в передаваемое сообщение ошибки, который передает сигнал в элемент настройки кратности автоматически подсчитываемых ошибок в канале связи.

|

|

|

Рисунок 9. Error_counter – счетчик с выходным сигналом в виде десятичного числа.

5. Структурная схема модели блока Priyem (рис.10).

Рисунок 10. Структурная схема модели блока Priyem.

Decoder_izb_code – декодер избыточного кода (рис11) предназначен для вычисления контрольных сумм модифицированного кода Хэмминга. Построен на элементах XOR (исключающее ИЛИ). Вычисление сумм происходит в соответствии с следующими формулами:

Рисунок 11. Декодер избыточного кода.

При появлении одиночной или двойной ошибки в хотя бы одной контрольной сумме на выходах 1 – 4 будет присутствовать единица. При отсутствии ошибок все контрольные суммы будут иметь значение «ноль».

Correction_block – схема коррекции информационных разрядов принятого сообщения в заданном помехозащитном коде. По условию задачи в моем варианте коррекция ошибок не производится. Поэтому схема будет иметь вид, представленный на рис. 12.

Рисунок 12. Схема коррекции информ. разрядов принятого сообщения.

Keys – схема распознавания одиночных и двойных ошибок представлена на рис. 13.

Рисунок 13. Схема распознавания одиночных и двойных ошибок.

При отсутствии ошибок на входах i1 – i4 в наличии логические нули (все контрольные суммы совпали) на выходе элемента NOR (ИЛИ-НЕ) логическая единица. Если одновременно с этим на входах k1 – k4 какое-либо слово в двоичном коде, то оно будет продублировано на выходных выводах k1 – k4 элементами AND (И). Если контрольные суммы не сходятся (наличие одной или 2-х ошибок), то на одном или нескольких входах i1 – i4 присутствует одна или несколько логических единиц. В этом случае на выходе элемента NOR (ИЛИ-НЕ) будет логический ноль, на выходных выводах k1 – k4 элементов AND (И) так же будет логический ноль. Передаваемое слово с ошибкой или ошибками не будет передано со входов на выходы схемы распознавания. При отсутствии ошибки на выходе blocking_signal будет «логическая единица», при наличии «логический ноль».

Analyzer – автоматический двоичный счетчик ошибок заданной кратности представлен на рис.14.

Рисунок 14. Автоматический двоичный счетчик

ошибок заданной кратности.

Анализатор осуществляет поразрядное сравнение передаваемых информационных разрядов и принятых (контрольные не учитываются). И подсчитывает в двоичном коде количество необнаруженных трансформаций заданной элементом Kratnost (рис. 2) кратности. Двоичный код отображается на индикаторе.

DC – дешифратор принятых команд представлен на рис.15. В данной схеме совмещены декодер обыкновенного двоичного кода, построенный на инверторах NOT (НЕ) и элементах конъюнкции AND (И). На элементах логического умножения Product производится перемножение логической единицы, соответствующей числу уставки на эталонное значение уставки. олученное десятичное значение через элемент ADD подается на контрольный осциллограф и локальную САР.

Рисунок 15. DC – дешифратор принятых команд

Экспериментальная часть

1. Запустим процесс симуляции всей системы SAR при отсутствии искажений в линии связи (период возмущений 25.6 сек). На экране виртуального осциллографа OU получим изображения (рис.21):

Рисунок 21. Результат работы локальной САР.

На рисунке сверху вниз изображены:

– принятые из линии связи значения уставок;

– реализованный процесс регулирования объекта регулирования;

– график ошибок;

– результат сравнения принятых и полученных значений уставок (0 отличий, что означает – схема функционирует верно).

2. Запустим процесс симуляции ошибок в линии связи

(период колебаний 0.05). Привести описание эксперимента (где менять параметры, откуда снимать показания и проч.)

Заполним таблицу, в которой представлены результаты подсчета необнаруженных трансформаций различной кратности.

Дата добавления: 2018-05-12; просмотров: 701; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!