Микропроцессор. Управляющий блок

Управляющий блок микропроцессора выполняет две основные функции:

- производит выборку команд программы в необходимом порядке из внешнего ЗУ;

- дешифрует выбранную команду и управляет выполнением микроопераций и микрокоманд в течение одного машинного цикла.

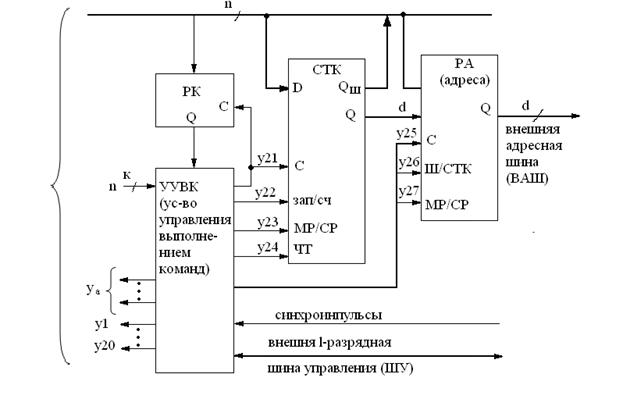

Для выполнения перечисленных функций в состав управляющего блока входят соответствующие аппаратные средства: счетчик команд (СТК), регистр адреса (РА), регистр команд (РК) и устройство управления выполнением команды (УУВК).

Рисунок – УБ МП.

Обрабатываемые данные и программа загружаются пользователем в основную память – ЗУ, которая является внешним по отношению к МП устройству. Данные из ЗУ поступают на внутреннюю шину МП через ШФ в виде n-разрядных слов. Для выборки необходимой команды МП должен обратиться к конкретной ячейке ЗУ, выставив на адресных входах ЗУ код этой ячейки. Эту операцию выполняет РА, к выходам которого подключена адресная шина. Так как данные и фрагменты программы могут храниться в любом месте ЗУ, то РА памяти должен иметь разрядность, не меньшую адресной разрядности ЗУ. Поэтому в МП разрядность РА больше длины слов данных. Например, в наиболее распространенных восьмиразрядных МП используется двухбайтовая (16-разрядная) адресная шина, позволяющая обращаться к 65536 ячейкам ЗУ.

Номер ячейки памяти, к которой требуется обращение, может находиться в различных узлах процессора. Поэтому при выборке данных из ЗУ адрес ячейки выставляется на шину данных и с нее переписывается в РА по управляющему сигналу Y25 (вход С регистра). При этом другой управляющий сигнал – Y26 (Ш/СТК) – устанавливает регистр в режим приема информации с шины (Ш), а не со счетчика (СТК). Так как разрядность шины данных меньше разрядности адреса, то запись адреса производится за два такта сначала младшие разряды, затем старшие (по управляющему сигналу Y27 «МР/СР»).

|

|

|

Адрес Ячейки ЗУ, в которой находится команда, вырабатывается счетчиком команд СТК, многоразрядный выход которого соединен напрямую с входом РА. Поэтому при выборке команд из ЗУ регистр адреса переводят в режим приема информации от счетчика (сигнал Y26) и сигналом Y25 переписывают содержимое СТК в РК.

Счетчик команд определяет очередность выборки команд из ЗУ. Команды в программе располагаются одна за другой в определенном порядке. Обычно каждая следующая команда имеет адрес, на единицу больший адреса предыдущей команды. Однако в случае ветвления программы или перехода к подпрограмме возникает необходимость обратиться к новому адресу, значительно отличающемуся от предыдущего. Таким образом, СТК должен подсчитывать количество сделанных шагов (выполненных команд) начиная с любого исходного адреса. В начале работы микропроцессора (по сигналу начальной установки) или в процессе работы (по командам условных и безусловных переходов) на внутренней шине данных выставляется некий исходный адрес начала нового фрагмента программы. Этот адрес поступает на входы параллельной записи СТК и по управляющему сигналу Y22 (режим «запись с входов») записывается в СТК. Так как разрядность шины данных меньше разрядности адреса, то запись исходного адреса производится за два такта (так же как и в РА). Затем СТК сигналом Y22 переводится в режим «счет импульсов с входа С» (СЧ) и последовательно подсчитывает количество выполненных команд в данном фрагменте программы. Отметим, что СТК имеет возможность передать адрес команды не только в РА, но и в шину данных (режим «чтение», сигнал Y24 и выход QШ), что позволяет использовать некоторые дополнительные способы адресации ЗУ.

|

|

|

Регистр команд (РК) предназначен для хранения кода выполняемой команды. Сменить информацию в этом регистре можно только после выполнения всех микрокоманд, составляющих текущую команду. Разрядность зависит от числа команд, выполняемых МП. Так как обычно число команд не превышает 200, то и длина слова регистра команд не превышает байта 128= 256 состояний.

|

|

|

Рассмотрим, как протекает процесс выборки из ЗУ адреса команды после включения микропроцессора.

Первый этап. Исходный адрес устанавливается на шине данных и переписывается в счетчик команд СТК.

Второй этап. С выхода СТК адрес переписывается в регистр адреса РА и по внешней адресной шине поступает на ЗУ.

Третий этап. По заданному адресу из ЗУ считывается необходимая команда и через шинный формирователь ШФ поступает в МП на внутреннюю шину данных.

Четвертый этап. С шины данных команда по сигналу Y21 переписывается в регистр команд РК. Этот же сигнал (Y21) увеличивает на единицу адрес команды, формируемой в СТК.

На этом заканчивается процесс выборки команды из ЗУ, называемый подциклом выборки, и МП переходит ко второму подциклу выполнению команды. В течение второй части машинного цикла операционный блок (под действием сигналов управления) выполняет все необходимые микрокоманды. Если при этом операционному блоку понадобятся какие-либо данные из ЗУ, то ОБ может воспользоваться РА (через шину данных) и выставить на адресной шине код необходимой ячейки ЗУ. Такое обращение к РА не изменяет содержимого РК и СТК и, следовательно, не нарушает выполнение текущей команды и порядок следования команд.

|

|

|

После завершения всех операций текущей команды начинается новый цикл. При этом второй и все следующие подциклы выборки будут короче первого, т.к. они начнутся со второго этапа записи в РК адреса, подготовленного СТК во время второй части предыдущего цикла.

После выборки команды из ЗУ она поступает в устройство управления выполнением команды УУВК.

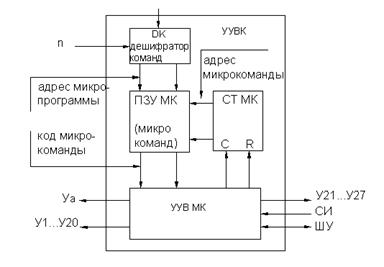

Устройство управления предназначено для организации необходимой последовательности действий всех остальных узлов микропроцессора. УУВК состоит из дешифратора команд ДК, устройства памяти микрокоманд ПЗУМК, счетчика микрокоманд СТМК и устройства управления выполнением микрокоманд УУВМК.

Дешифратор команд DК расшифровывает код команды с учетом признаков П выполнения логических условий в предыдущем машинном цикле (при выполнении предыдущей команды). Преобразованный многоразрядный код команды поступает на ПЗУМК, в котором хранятся микропрограммы выполнения всех команд. Выбор необходимой микропрограммы осуществляется кодом, поступающим от DК, а пошаговое исполнение микропрограммы управляется счетчиком микрокоманд. СТМК получает единичное приращение после выполнения очередной микрооперации и обнуляется при окончании последнего машинного такта, заданного кодом команды.

Устройство управления выполнением микрокоманд УУВМК формирует последовательность сигналов, управляющих микрооперациями, необходимыми для выполнения данной микрокоманды. Эта последовательность формируется в пределах одного машинного такта и обычно является многофазной (2…4 фазы). Временные границы такта и фазы управляющих сигналов задаются синхроимпульсами (СИ), которые или генерируются внутри УУВК, или поступают от внешнего генератора синхросигналов. Пример образования двухфазной последовательности СИ показан на рисунке

Рис. Последовательность СИ.

Благодаря многофазности синхросигналов в одном такте микропроцессора может совершаться несколько последовательных групп событий.

Схематически УУВМК представляет собой набор формирователей управляющих сигналов, фазы и длительность которых согласованы с синхроимпульсами. Количество формирователей определяется числом управляющих сигналов, выходящих из УУВМК. Разрешение на работу того или иного формирователя в данном такте поступает от ПЗУМК в виде кода микрокоманды.

Хранение микропрограмм в специальном ПЗУ позволяет вносить изменения в систему команд микропроцессора и на основе одной и той же базовой БИС получать специализированные устройства обработки данных, ориентированные на выполнение различных задач, чтобы предусмотреть такую возможность не только разработчику, но и пользователю МП. Устройство памяти можно выполнять в виде перепрограммируемого ПЗУ. Такое ППЗУ встраивается в БИС микропроцессора и дает возможность потребителю записать в него необходимую систему команд.

Если же специализация МП не требуется и система команд жестко определена разработчиком, то ПЗУ можно заменить дешифратором микрокоманд DМК. Такая замена усложняет структуру УУВМК, но увеличивает быстродействие микропроцессора. Ы современных МП применяются оба способа построения УУВК как с микропрограммным ЗУ, так и с жесткой логикой.

Вопрос 12

Дата добавления: 2018-04-15; просмотров: 726; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!