Логические элементы

Любой символ информации в цифровых устройствах кодируют в двоичном алфавите, поэтому сигналы могут принимать только два значения:

высокий или низкий уровень напряжения, наличие или отсутствие импульса напряжения и т. д. Обязательным условием при этом является возможность уверенного распознавания элементами цифровых схем двух значений сигналов» соответствующих символам 0 и 1, в условиях изменения температуры окружающей среды, напряжения источника питания, воздействия других дестабилизирующих факторов.

высокий или низкий уровень напряжения, наличие или отсутствие импульса напряжения и т. д. Обязательным условием при этом является возможность уверенного распознавания элементами цифровых схем двух значений сигналов» соответствующих символам 0 и 1, в условиях изменения температуры окружающей среды, напряжения источника питания, воздействия других дестабилизирующих факторов.

В дискретных устройствах используют два способа представления информации: потенциальный и импульсный. При потенциальном способе значениям логического 0 и логической 1 соответствуют напряжения низкого и высокого уровня. Если логическому 0 соответствует напряжение низкого уровня, а логической 1 — высокого, то такую логику называют положительной, и наоборот, если за логический 0 принимают напряжение высокого, а за логическую 1 — напряжение низкого уровня, то такую логику называют отрицательной. В дальнейшем будем рассматривать устройства только с положительной логикой.

Информация в цифровых устройствах может быть представлена в последовательном и параллельном кодах. При использовании последовательного кода каждый такт соответствует одному разряду двоичного кода. Номер разряда определяется номером такта, отсчитываемого от такта, совпадающего с началом представления кода.Графики, показанные на рис. 2, иллюстрируют последовательный код байтового двоичного числа 10011011 при потенциальном и импульсном способах представления информации. При первом способе (рис. 2,а) сигнал сохраняет низкий или высокий уровни в течение одного или нескольких тактов. В моменты перехода сигнала от одного уровня к другому его значение является неопределенным. При импульсном способе представления цифровой информации (рис. 2,6) единичному и нулевому значению двоичной переменной соответствует наличие или отсутствие импульса конечной длительности. При последовательном коде числа все его разряды могут быть зафиксированы на одном элементе и переданы по одному каналу передачи информации. Для передачи всего числа требуется восемь тактов (рис. 2,в).

|

|

|

Параллельный код позволяет существенно сократить время обработки и передачи информации. Для примера рис. 3 иллюстрирует параллельный код семиразрядного числа 1101101. В этом случае как при импульсном (рис. 3,а), так и при потенциальном (рис. 3,б) способах представления информации все разряды двоичного кода представлены в одном временном такте, могут фиксироваться отдельными элементами и передаваться по раздельным каналам (разрядным шинам).

|

|

|

ОСНОВНЫЕ ЭЛЕМЕНТЫ АЛГЕБРЫ ЛОГИКИ

Анализ комбинационных устройств и цифровых автоматов проще всего проводить с помощью алгебры логики, оперирующей только с двумя понятиями: истинным (логическая 1) и ложным (логический 0). В результате функции, отображающие информацию, принимают в каждый момент времени только значения 0 или 1. Такие функции называют логическими. Логические функции V нескольких переменных (ХО, Х1,...,Хп—1) определяют характер логических операций, в результате которых набору входных переменных ставится в соответствие переменная У

Y = f (Х0, X1,..., Хn—1).

Наиболее наглядно функция преобразования характеризуется таблицей, в строках которой каждой комбинации входных переменных Х соответствует значение выходной переменной Y. Ее называют таблицей истинности.

| Таблица 3 | ||

| X1 | Х2 | Y = Х1∙Х2 |

Функция У1 = Х1 ∙ Х2 принимает значение логической 1 только при равенстве 1 всех входных переменных. Если хоть одна переменная равна 0, то и выходная функция равна нулю (табл. 3).

В зависимости от способа представления двоичной информации элементы ЭВМ делятся соответственно на потенциальные, импульсные и импульсно-потенциальные. Наибольшее распространение получили потенциальные элементы, которые отличаются технологичностью интегрального исполнения, меньшей чувствительностью к помехам, высокой надежностью в работе и т. д. Следует отметить, что импульсные элементы требуют строгой синхронизации информационных сигналов, так как в противном случае может нарушиться их физическое взаимодействие во времени

|

|

|

Дадим общую характеристику логическим и запоминающим элементам ЭВМ.

Дадим общую характеристику логическим и запоминающим элементам ЭВМ.

Логические элементы обеспечивают реализацию различных логических функций от входных двоичных переменных, например функций И, ИЛИ и НЕ. Названные функции образуют функционально полный набор, поэтому с помощью таких элементов можно построить любые сложные комбинационные схемы. Однако в ряде случаев проще реализовать некоторые логические схемы с использованием более сложных логических элементов, например элементов И-НЕ, ИЛИ-НЕ, И-ИЛИ-НЕ, каждый из которых также образует функционально полный набор, обеспечивающий построение любых комбинационных схем.

В таблице приведены условные обозначения некоторых типовых логических элементов и реализуемые ими логические функции.

|

|

|

Выход элемента обозначается кружком, если им реализуется функция с инверсией (отрицанием); вход также отмечается кружком, если функция реализуется при инверсном значении соответствующей входной переменной.

Логические элементы обычно выпускаются в виде микросхем малой и средней степени интеграции, в которых реализуются разнообразные совокупности логических операций, таких, как И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ, И-ИЛИ-НЕ и др.

ТРИГГЕРЫ И ИХ ХАРАКТЕРИСТИКИ

Простейшими цифровыми автоматами с памятью являются триггеры. Триггер — это устройство последовательного типа с двумя устойчивыми состояниями равновесия, предназначенное для записи и хранения информации. Под действием входных сигналов триггер может переключаться из одного устойчивого состояния в другое. При этом напряжение на его выходе скачкообразно изменяется.

Как правило, триггер имеет два выхода: прямой и инверсный. Число входов зависит от структуры и функций, выполняемых триггером. По способу записи информации триггеры делят на асинхронные и синхронизируемые (тактируемые). В асинхронных триггерах информация может записываться непрерывно и определяется информационными сигналами, действующими на входах в данный момент времени. Если информация заносится в триггер только в момент действия так называемого синхронизирующего сигнала, то такой триггер называют синхронизируемым или тактируемым. Помимо информационных входов синхронизируемые триггеры имеют тактовый вход (вход синхронизации). В цифровой технике приняты следующие обозначения входов триггеров:

S — раздельный вход установки в единичное состояние (напряжение высокого уровня на прямом выходе 0);

R — раздельный вход установки в нулевое состояние (напряжение низкого уровня на прямом выходе 0);

D — информационный вход (на него подается информация, предназначенная для занесения в триггер);

С — вход синхронизации;

Т — счетный вход.

Наибольшее распространение в цифровых устройствах получили RS-триггер с двумя установочными входами, тактируемый 0-триггер и счетный Т-триггер. Рассмотрим функциональные возможности каждого из них.

Асинхронный RS-триггер. В зависимости от логической структуры различают RS-триггеры с прямыми и инверсными входами. Их схемы и условные обозначения приведены на рис. 12. Триггеры такого типа построены на двух логических элементах: 2ИЛИ—НЕ — триггер с прямыми входами (рис. 12,а), 2И—НЕ — триггер с инверсными входами (рис. 12,б). Выход каждого из элементов подключен к одному из входов другого элемента, что обеспечивает триггеру два устойчивых состояния. Здесь приведены таблицы истинности для каждого из этих триггеров.

Асинхронный RS-триггер. В зависимости от логической структуры различают RS-триггеры с прямыми и инверсными входами. Их схемы и условные обозначения приведены на рис. 12. Триггеры такого типа построены на двух логических элементах: 2ИЛИ—НЕ — триггер с прямыми входами (рис. 12,а), 2И—НЕ — триггер с инверсными входами (рис. 12,б). Выход каждого из элементов подключен к одному из входов другого элемента, что обеспечивает триггеру два устойчивых состояния. Здесь приведены таблицы истинности для каждого из этих триггеров.

| Таблица 8 | |||||

| S | R | Qt | _ Qt | Qt+1 | _ Qt+1 |

| * | * | ||||

| * | * |

| Таблица9 | |||||

| _ S | _ R | Qt | _ Qt | Qt+1 | _ Qt+1 |

| * | * | ||||

| * | * | ||||

В таблицах Qt и Ōt обозначают уровни, которые были на выходах триггера до подачи на его входы так называемых активных уровней. Активным называют логический уровень, действующий на входе логического элемента и однозначно определяющий логический уровень выходного сигнала (независимо от логических уровней, действующих на остальных входах). Для элементов ИЛИ — НЕ за активный уровень принимают высокий уровень, а для элементов И — НЕ — низкий уровень. Уровни, подача которых на один из входов не приводит к изменению логического уровня на выходе элемента, называют пассивными. Уровни Qt+1 и Ōt+1обозначают логические уровни на выходах триггера после подачи информации на его входы.

Для триггера с прямыми входами Qt+1 = 1 при S = 1 и R=0; Qt+1 = 0 при S = 0 и R = 1; Qt+1 = Qt при S = 0 и R = 0. При R = S = 1 состояние триггера будет неопределенным, так как во время действия информационных сигналов логические уровни на выходах триггера одинаковы (Qt+1 = Ōt+1 = 0), а после окончания их действия триггер может равновероятно принять любое из устойчивых состояний. Поэтому такая комбинация является запрещенной.

Для триггера с прямыми входами Qt+1 = 1 при S = 1 и R=0; Qt+1 = 0 при S = 0 и R = 1; Qt+1 = Qt при S = 0 и R = 0. При R = S = 1 состояние триггера будет неопределенным, так как во время действия информационных сигналов логические уровни на выходах триггера одинаковы (Qt+1 = Ōt+1 = 0), а после окончания их действия триггер может равновероятно принять любое из устойчивых состояний. Поэтому такая комбинация является запрещенной.

Режим S = 1, R = 0 называют режимом записи 1 (так как Qt+1 = 1); режим S = 0 и R = 1—режимом записи 0. Режим S = 0, R = 0 называется режимом хранения информации, так как информация на выходе остается неизменной. Для триггера с инверсными входами режим записи логической 1 реализуется при S = 0, R = 1, режим записи логического 0 — при S = 1, R = 0. При S = R = 1 обеспечивается хранение информации. Комбинация S = R = 0 является запрещенной.

Следует, однако, отметить, что самостоятельно RS-триггеры в устройствах цифровой техники практически не используются из-за их низкой помехоустойчивости.

Тактируемый D-триггер. Он имеет информационный выход и вход синхронизации. Одна из возможных структурных схем однотактного D-триггера и его условное обозначение показаны на рис. 13. Если уровень сигнала на входе С = 0, состояние триггера устойчиво и не зависит от уровня сигнала на информационном входе.

При этом на входы RS-триггера с инверсными входами (элементы.3 и 4) поступают пассивные уровни (8==К==1). При подаче на вход синхронизации уровня С=1 информация на прямом выходе будет повторять информацию, подаваемую на вход D. Таким образом, при С = 0 Qt+1 = Qt, а при С = 1 Qt+1 = D. Таблица истинности тактируемого D-триггера имеет вид:

| Таблица 10 | ||

| D | Q | Qt+1 |

Здесь Qt означает логический уровень на прямом выходе до подачи импульса.синхронизации, а Qt+1 — логический уровень на этом выходе после подачи импульса синхронизации.

На рис. 14 изображены временные диаграммы тактируемого 0-триггера. В таком триггере происходит задержка сигнала на выходе по отношению к сигналу, поданному па вход, на время паузы между синхросигналами. Для устойчивой работы триггера необходимо, чтобы в течение синхроимпульса информация на входе была неизменной.

На рис. 14 изображены временные диаграммы тактируемого 0-триггера. В таком триггере происходит задержка сигнала на выходе по отношению к сигналу, поданному па вход, на время паузы между синхросигналами. Для устойчивой работы триггера необходимо, чтобы в течение синхроимпульса информация на входе была неизменной.

Тактируемые D-триггеры могут быть с потенциальным и динамическим управлением. У первых из них информация записывается в течение времени, при котором уровень сигнала С = 1. В триггерах с динамическим управлением информация записывается только в течение перепада напряжения на входе синхронизации. Динамические входы изображают на схемах треугольником. Если вершина треугольника обращена в сторону микросхемы, то триггер «срабатывает» по фронту входного импульса, если от нее — по срезуим пульса. В таком триггере информация на выходе может быть задержана на один такт по отношению к входной информации.

Счетный Т-триггер (рис. 15,а). Его называют также триггером со счетным входом. Он имеет один управляющий вход Т и два выхода Q и Ō,. Информация на выходе такого триггера меняет свой знак на противоположный при каждом положительном (или при каждом отрицательном) перепаде напряжения на входе. В сериях выпускаемых микросхем Т-триггеров, как правило, нет. Но триггер такого типа может быть создан на базе тактируемого D-триггера, если его инверсный выход соединить с информационным входом (рис. 15,б). Как видно из диаграммы на рис. 15,в, частота сигнала на выходе Т-триггера в два раза ниже частоты сигнала на входе, поэтому такой триггер можно использовать как делитель частоты и двоичный счетчик.

В сериях выпускаемых микросхем есть также универсальные JK-триггеры. При соответствующем подключении входной логики JK-триггер может выполнять функции триггера любого другого типа.

ОСНОВНЫЕ УЗЛЫ ЦИФРОВЫХ УСТРОЙСТВ

РЕГИСТРЫ

Несколько триггеров можно объединить в регистр — узел для хранения чисел с двоичным представлением цифр разрядов. Основными видами регистров являются параллельные и последовательные (сдвигающие).

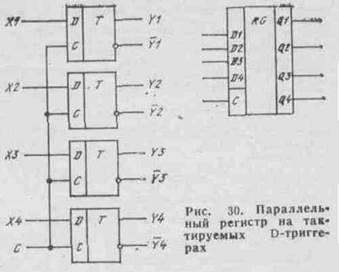

В параллельном регистре на тактируемых D-триггерах (рис. 30) код запоминаемого числа подается на информационные входы всех триггеров и записывается в регистр с приходом тактового импульса. Выходная информация изменяется с подачей нового входного слова и приходом следующего импульса записи. Такие регистры используют в системах оперативной памяти. Число триггеров в них равно максимальной разрядности хранимых слов.

В параллельном регистре на тактируемых D-триггерах (рис. 30) код запоминаемого числа подается на информационные входы всех триггеров и записывается в регистр с приходом тактового импульса. Выходная информация изменяется с подачей нового входного слова и приходом следующего импульса записи. Такие регистры используют в системах оперативной памяти. Число триггеров в них равно максимальной разрядности хранимых слов.

Схема последовательного регистра и временная диаграмма, иллюстрирующая его работу, приведены на рис. 31. По приходу тактового импульса С первый триггер записывает код Х (0 или 1), находящийся в этот момент на его входе D, а каждый следующий триггер переключается в состояние, в котором до этого находился предыдущий. Так происходит потому, что записываемый сигнал проходит со входа D триггера к выходу Q с задержкой, большей длительности фронта тактового импульса (в течение которого происходит запись), Каждый тактовый импульс последовательно сдвигает код числа в регистре на один разряд. Поэтому для записи N-разрядного кода требуется N тактовых импульсов. На диаграмме видео. что четырехразрядное число 1011 было записано в соответствующие разряды регистра (1 — Q4, 0 — Q3, 1 — Q2, 1 — Q1) после прихода четвертого тактового импульса. До прихода следующего тактового импульса это число хранится в регистре в виде параллельного кода на выходах Q4 — Q1. Если необходимо получить хранимую информацию в последовательном коде, то ее снимают с выхода Q4 в моменты прихода следующих четырех импульсов (5—9). Такой режим называется режимом последовательного считывания.

Очень удобны универсальные регистры, позволяющие производить как последовательную, так и параллельную запись и считывание. Такие регистре можно использовать в качестве преобразователей параллельного кода в последовательный и обратно. Например, микросхема К155ИР1 — четырехразрядный универсальный сдвиговый регистр. Регистр работает в режиме сдвига по тактовым импульсам, поступающим на вход С1, если на входе V2 имеется напряжение низкого уровня. Вход V1 служат для ввода информации в первый разряд регистра в этом режиме. Если же на входе У2 напряжение высокого уровня, то регистр производит параллельную запись информации со входов D1—D4 по импульсам синхронизации, поступающим на вход С2.

СЧЕТЧИКИ

Счетчиком называют устройство, предназначенное для подсчета числа импульсов, поданных на вход. Они, как и сдвигающие регистры, состоят из цепочки триггеров. Разрядность счетчика, а следовательно, и число триггеров определяется максимальным числом, до которого он считает.

Регистр сдвига можно превратить в кольцевой счетчик, если выход последнего триггера соединить с входом D первого. Перед началом счета импульсом начальной установки в нулевой разряд счетчика (Q0) записывается логическая 1, в остальные разряды — логические 0. С началом счета каждый из приходящих счетных импульсов Т перезаписывает 1 в следующий триггер, и число поступивших импульсов определяется по номеру выхода, на котором имеется 1. Предпоследний (N — 1) импульс переведет в единичное состояние последний триггер, а N импульс перенесет это состояние на выход нулевого триггера, и счет начнется сначала. Таким образом, можно построить кольцевой счетчик с произвольным коэффициентом счета (любым основанием счисления), изменяя лишь число триггеров в цепочке.

Недостаток такого счетчика — большое число триггеров, необходимых для его построения. Более экономичны, а поэтому и более распространены счетчики, образованные счетными Т-триггерами. После каждого тактового импульса Т сигнал на входе D (инверсном выходе) меняется на противоположный и поэтому частота выходных импульсов вдвое меньше частоты поступающих. Собрав последовательную цепочку из n счетных триггеров (соединяя выход предыдущего триггера со входом С следующего), мы получим частоту fвых = fвх/2n. При этом каждый входной импульс меняет код числа на выходе счетчика на 1 в интервале от 0 до N = 2n - 1.

Микросхема К155ИЕ5 (рис. 34) содержит счетный триггер (вход С1) в делитель на восемь (вход С2), образованный тремя соединенными последовательно триггерами. Триггеры срабатывают по срезу входного импульса (по переходу из 1 в 0). Если соединять последовательно все четыре триггера (как на рис. 34), то получится счетчик по модулю 24 = 16. Максимальное хранимое в счетчике число при полном заполнении его единицами равно N = 24 – 1 = 15 = (1111)2. Такой счетчик работает с коэффициентом счета К (модулем), кратным целой степени 2, и в нем совершается циклический перебор К==2n устойчивых состояний. Счетчик имеет входы принудительной установки в 0.

Часто нужны счетчики с числом устойчивых состояний, отличным от 2n. Например, в электронных часах есть микросхемы с коэффициентом счета 6 (десятки минут), 10 (единицы минут), 7 (дни недели), 24 (часы). Для построения счетчика с модулем К ≠ 2n можно использовать устройство из n триггеров, для которого выполняется условие 2n > К. Очевидно, такой счетчик

Часто нужны счетчики с числом устойчивых состояний, отличным от 2n. Например, в электронных часах есть микросхемы с коэффициентом счета 6 (десятки минут), 10 (единицы минут), 7 (дни недели), 24 (часы). Для построения счетчика с модулем К ≠ 2n можно использовать устройство из n триггеров, для которого выполняется условие 2n > К. Очевидно, такой счетчик  может иметь лишние устойчивые состояния (2n - К). Исключить эти ненужные состояния можно использованием обратных связей, по цепям которых счетчик переключается в нулевое состояние в том такте работы, когда он досчитывает до числа К.

может иметь лишние устойчивые состояния (2n - К). Исключить эти ненужные состояния можно использованием обратных связей, по цепям которых счетчик переключается в нулевое состояние в том такте работы, когда он досчитывает до числа К.

Дата добавления: 2016-01-05; просмотров: 16; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!