Исследовать функционирование двухтактных триггеров и триггеров с динамическим управляющим входом

Таблица 1 - Варианты задания (выдается преподавателем)

| № варианта | Тип триггера | Номер рисунка |

| 1 | Двухтактный RS-триггер | Рисунки 4 и 5 |

| 2 | -//- D-триггер | Рисунок 6 |

| 3 | -//- T-триггер | Рисунок 7 |

| 4 | -//- JK-триггер | Рисунок 8 |

| 5 | Однотактный с динамическим управляющим входом RS-триггер | Рисунок 9 |

| 6 | -//- D-триггер | Рисунок 10 |

| 7 | -//- T-триггер | Рисунок 11 |

| 8 | -//- JK-триггер | Рисунок 12 |

Рисунок 4 - Двухтактный RS-триггер

Рисунок 5 - Триггер с запрещающими связями

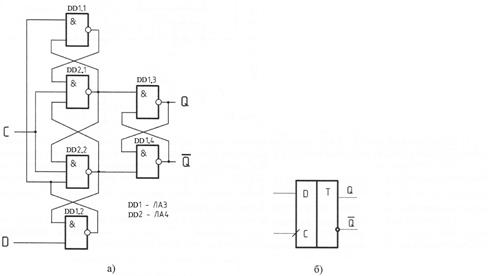

Рисунок 6 - Условное обозначение и схема двухтактного D-триггера

Рисунок 7 - Условное обозначение, схема и временные диаграммы Т-триггера

с запрещающими связями

Рисунок 8 - Схема и условное обозначение двухтактного JK-триггера

Рисунок 9 - Схема и условное обозначение синхронного RS-триггера с

динамическим управляющим входом

|

|

|

Рисунок 10 - Схема и условное обозначение синхронного D-триггера

Рисунок 11 - Схема, условное обозначение и временные диаграммы Т-триггера

на бистабильных ячейках

Рисунок 12 - Синхронный JK-триггер с динамическим управляющим входом

Определите, какие управляющие импульсы (единичные или нулевые) требуются для записи информации в триггер и подключите вход С триггера к соответствующее выходу ГОИ.

Осуществите управление режимами работы триггера в последовательности, заданной преподавателем. Фиксируйте моменты изменения состояния триггера с помощью осциллографа.

Контрольные вопросы

1.Что называется триггером? _______________________________________________

_________________________________________________________________________

2. Назовите основные режимы работы триггеров. __________________________________________________________________________________________________________________________________________________

3.Каким образом можно получит синхронный RS- триггер? ___________________________________________________________________________________________________________________________________________________________________________________________________________________________

4. Основное назначение D триггеров _________________________________________________________________________________________________________________________________________________ 5. Каким образом можно получить Т-триггер из JK- триггера? Возможно ли это? __________________________________________________________________________________________________________________________________________________

|

|

|

6. Каким образом можно получить двухтактный D – триггер из двухтактного RS – триггера? Возможно ли это? ___________________________________________________________________________________________________________________________________________________________________________________________________________________________

Лабораторная работа № 6

«Исследование многоразрядного комбинационного сумматора»

Учебная цель: научиться исследовать сумматоры.

Учебные задачи:

1. Исследование функционирования двоичного четырехразрядного комбинационного сумматора.

Краткие теоретические и учебно-методические материалы по теме лабораторной работы

Сумматоры — устройства, предназначенные для выполнения основной арифметической операции - суммирования (сложения) чисел в двоичном коде. Простейший случай — это суммирование двух одноразрядных чисел: 0 + 0 = 0; 1 + 0 = 1; 1 + 1 = 10. В последнем случае выходное двоичное число 10 (соответствует десятичному числу 2) оказалось двухразрядным. Появившаяся в старшем разряде суммы единица называется единицей переноса.

Различают полусумматоры и полные сумматоры. Полные сумматоры в отличие от полусумматоров имеют вход для приёма сигнала переноса из предыдущего младшего разряда.

|

|

|

Условное обозначение одноразрядного полного сумматора приведено на рисунке 1. Сигналы на его выходах (суммы S и выходе переноса в следующий старший разряд С n +1) получаются в результате сложения трёх входных сигналов (на входах слагаемых А и В и входе переноса из предыдущего младшего разряда С n). В таблице 1 представлены все возможные комбинации двоичных одноразрядных слагаемых А и В и сигнала переноса С n.

Полные сумматоры многоразрядных чисел составляются из полных сумматоров одноразрядных чисел. Они могут выполнять суммирование многоразрядных чисел двумя способами: параллельным или последовательным.

Дата добавления: 2019-07-17; просмотров: 190; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!