И ее связь с основной программой

Рисунок 14.8 – Формирование векторов прерывания в контроллере ВУ

Рисунок 14.9 – Реализация приоритетов ВУ в микроЭВМ с векторной системой прерываний с интерфейсным вектором (ППР (вх.) - "Предоставление прерывания (входной)"; "ППР (вых.) - Предоставление прерывания (выходной)")

Рисунок 14.10 – Контроллер прерываний Intel 8259A

Рисунок 2.2 – Типичная трехшинная структура МПС

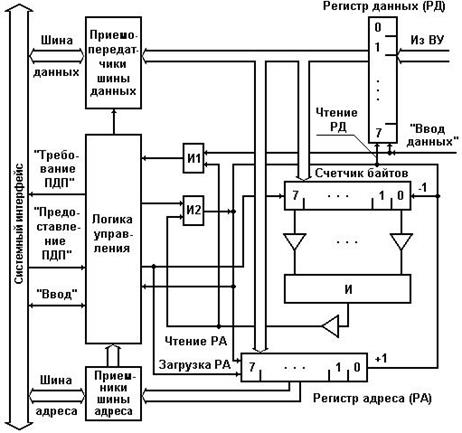

Рисунок 14.11 – Контроллер ПДП для ввода данных из ВУ в режиме "Захват цикла" и отключением процессора от шин системного интерфейса

Рисунок 14.12 – Составные части МПС, подключенные к ШД

С помощью шинных формирователей

Рисунок 14.13 – Организация подключения к системной ШД МП,

Памяти и устройств ввода/вывода с использованием ШФ

Рисунок 15.1 – Классификация современных полупроводниковых ЗУ

Рисунок 15.2 – Типовая структура полупроводниковой микросхемы ЗУ

Рисунок 15.3 – Микросхемы ОЗУ (К573РУ9) и

ППЗУ (К573РФ5) в составе микропроцессорной системы

Рисунок 15.4 – Пример взаимодействия программируемых ИМС параллельного порта (PI) КР580ВВ55А и таймера (T) КР580ВИ53

С системной магистралью компьютера; DC - дешифратор К555ИД7

Рисунок 15.6 – Структурная схема буфера 64×4

Рисунок 15.7 – Принцип работы стековой памяти

|

|

|

|

|

|

| |

|

Рисунок 15.8 – Стек: а) организация стека в ОЗУ; б) процессы при записи в стек; в) процессы при чтении из стека | |

Рисунок 15.9 – Структурная схема МП,

Содержащая буфер команд и буфер операндов

Рисунок 15.10 – Структура кэшированной памяти

Рисунок 16.2 – Модульная организация МК

Рисунок 16.3 – Структура микроконтроллера AVR типа AT 90 S 8515

Рисунок 16.4 – Структура порта ввода/вывода микроконтроллера AVR

Рисунок 17.1 – Типовая схема двунаправленного порта ввода/вывода МК

Рисунок 17.2 – Структура 16-разрядного модуля таймера/счетчика

Рисунок 17.3 – Структура процессора событий МК семейства Intel 8xC51Fx

Рисунок 19.1 – Классификация языков программирования

Рисунок 19.2 – Преобразование исходной программы в выполняемый загрузочный модуль: ИМ, ОМ, ЗМ – исходный, объектный,

Загрузочный модуль

Рисунок 19.6 – Блок-схема конструкции управления «вызов подпрограммы»

Рисунок 20.2 – Структурная схема ГСПФ на основе

Цифрово го синтезатора сигналов (ЦСС) с микропроцессором

Рисунок 20.3 – Обобщенная структурная схема АСК

|

|

|

Рисунок 20.4 – Модель вычислительного ядра МПС

Рисунок 20.5 – Структурная схема адаптивной системы контроля РЭС

Рисунок 21.2 – Структурная схема приемника

С микропроцессорным демодулятором

Рисунок 21.3 – Структура узла коммутации

Рисунок 21.4 – Структура одноканальной системы

Автоматического управления технологическим процессом

Рисунок 21.5 – Организация сигнала управления

Рисунок 21.6 – Основные этапы разработки контроллера

Рисунок 22.1 – Основные разделы цифровой обработки сигналов

Рисунок 22.4 – Обобщенная структурная схема ЦОС

Рисунок 22.5 – Временные диаграммы сигналов при ЦОС

Рисунок 22.7 – Обработка аналоговых и цифровых сигналов

Таблица 22.1 – Классификация сигналов

Таблица 22.2 – Сигналы играющие важную роль в радиоэлектронике

Рисунок 23.2 – Графики перехода от аналогового

непрерывного сигнала  к дискретному

к дискретному

Рисунок 23.3 – Графики непрерывного  и дискретного сигнала

и дискретного сигнала  их спектров

их спектров  и

и

Рисунок 23.15 – Пример трехпозиционного сигнала

|

|

|

Рисунок 23.16 – АКФ сигнала, представленного на рисунке 23.15

Таблица 24.1 – Численные значения для примера усреднения

| Индекс минуты | Количество машин за последнюю минуту | Среднее за последние 5 минут количество машин в минуту |

| 1 | 10 | - |

| 2 | 22 | - |

| 3 | 24 | - |

| 4 | 42 | - |

| 5 | 37 | 27 |

| 6 | 77 | 40,4 |

| 7 | 89 | 53,8 |

| 8 | 22 | 53,4 |

| 9 | 63 | 57,6 |

| 10 | 9 | 52 |

Рисунок 24.7 – Усреднение количества машин в минуту

Рисунок 24.8 – Структура усредняющего фильтра в момент,

Дата добавления: 2022-12-03; просмотров: 20; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!